分频器是伴随着频率综合器的出现而发展起来的,在射频无线收发芯片中需要频率综合器输出高质量的本地载波来完成信号的上变频或下变频;在数字芯片中需要频率综合器输出各种不同频率的时钟来驱动时序电路完成各种逻辑运算。频率综合器中都需要分频器来讲高频时钟分频至低频时钟的任务。

分频器

分频器可分为:

- 模拟分频器

- 数字分频器

| 模拟分频器 | 数字分频器 | |

|---|---|---|

| 工作频率 | 高 | 低 |

| 工作范围 | 窄 | 宽 |

| 实现方式 | 复杂 | 简单 |

| 功耗 | 较大 | 正比工作频率 |

| 工艺角及温度影响 | 较大 | 较小 |

| 随工艺发展的潜力 | 较小 | 较大 |

下文主要介绍数字分频器。

数字分频器

数字分频器是基于锁存器(Latch)所存数据的原理,在输入时钟的使能下完成对输入时钟的分频。

D 锁存器

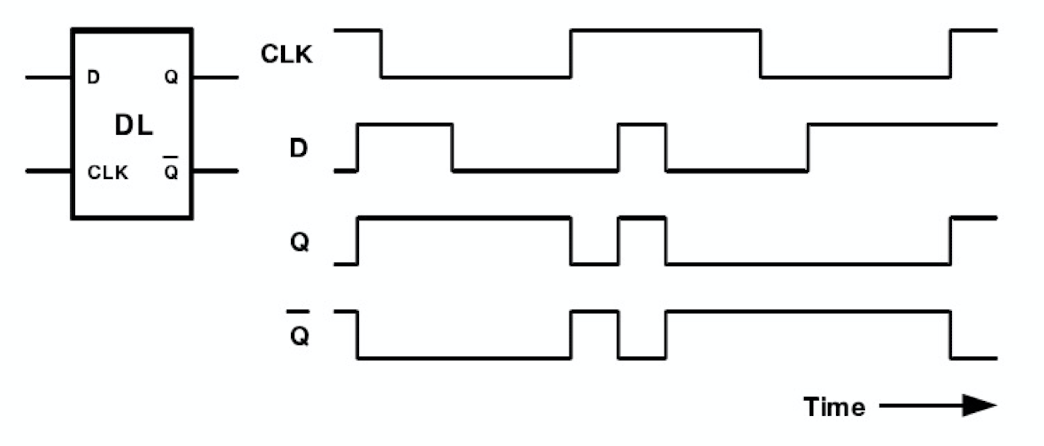

D 锁存器的数据输出在时钟输入端为高电平时,跟随数据输入端;在时钟输入端为低电平时,一直锁存当前数据保持不变。

主从锁存器

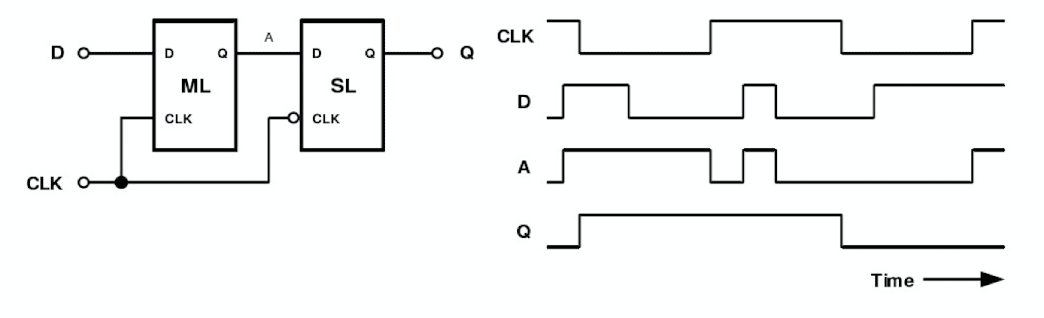

锁存器的数据输出端在时钟时钟输入端为高电平时一直跟随数据输入端的变化而变化会引起一系列诸如不稳定、毛刺和竞争冒险等时序问题。可以使用由两个相位互反的时钟分别驱动两个串联的 D 锁存器来解决。

亚稳态/稳定性分析

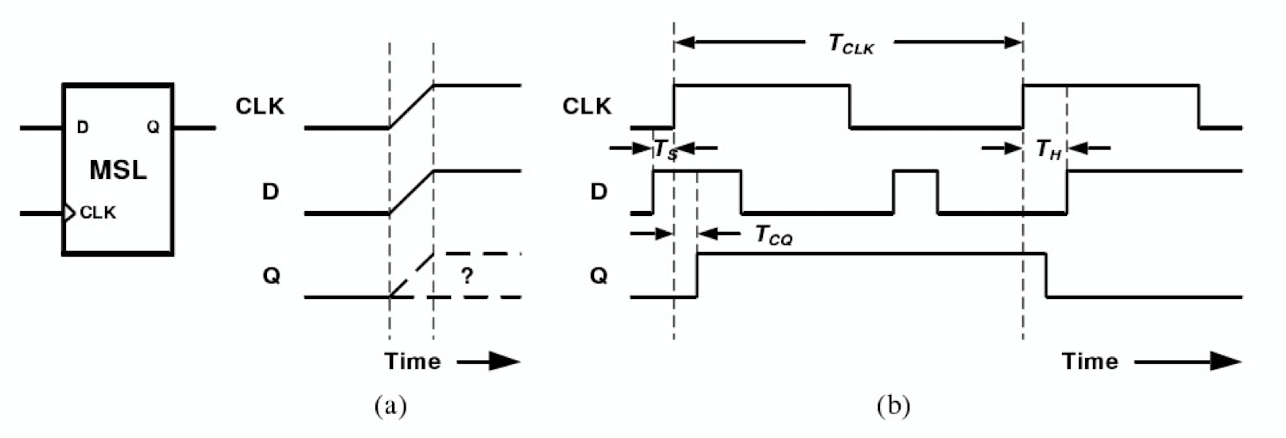

如图(a)所示,在时钟上升沿,数据输入发生变化,那么数据输出该如何变化。此时就产生了亚稳态问题。

主从锁存器的实际时序图如图(b)所示:

- \(T_{CLK}\) :时钟输入端的时钟周期;

- \(T_S\) :建立时间(Set-up Time),为数据输入端在时钟输入端上升沿来临前的建立时间;

- \(T_H\) :保持时间(Hold Time),为数据输入端在时钟输入端上升沿来临前的保持时间;

- \(T_{CQ}\) :时钟输入端到数据输出端的时延(CLK-to-Q Delay),决定了 \(T_S\) 和 \(T_H\) 的最小值;

为保证锁存器工作的稳定性,需要满足如下条件:

- \(T_{CLK}\) 大于锁存器的最小出入时钟周期;

- 数据输入端在 \(T_S\) 之前建立完毕,并保持到 \(T_H\) 之后;

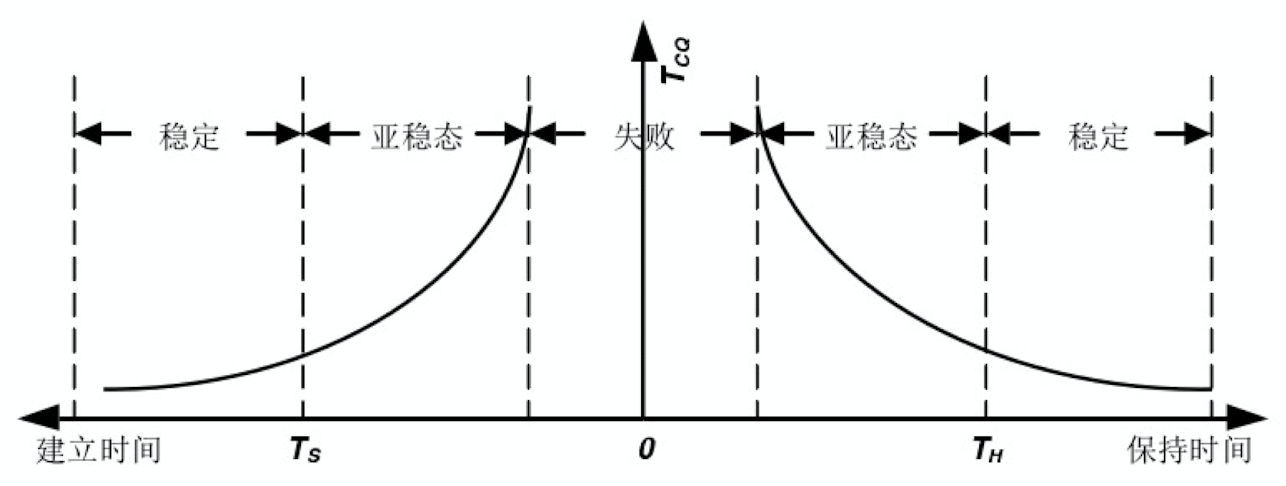

时序关系如下图所示:

正交二分频器的结构

目前已有很多种结构的锁存器被发明出来做分频电路,下文介绍几种具有代表性的锁存器结构。

传输门主从锁存器

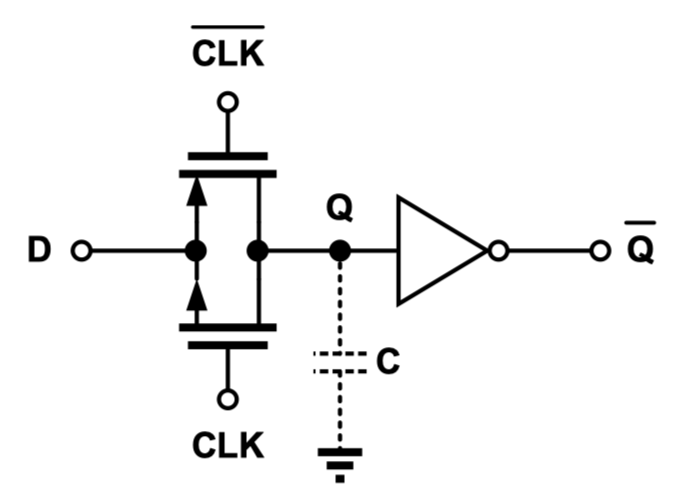

基本的传输门锁存器如上图所示,一对互补的 MOS 管组成了一个传输门开关。

- CLK为高电平时,传输门打开,输入信号 D 存储至电容 C 中;

- CLK由高变低时,传输门关闭,电容 C 存储的电荷继续维持锁存器的输出。

实际中电容 C 可以用传输门和反相器的寄生电容来实现,但由于传输门关闭后仍有微小的漏电流存在,传输门寄存器需要定期刷新来保证数据不丢失。

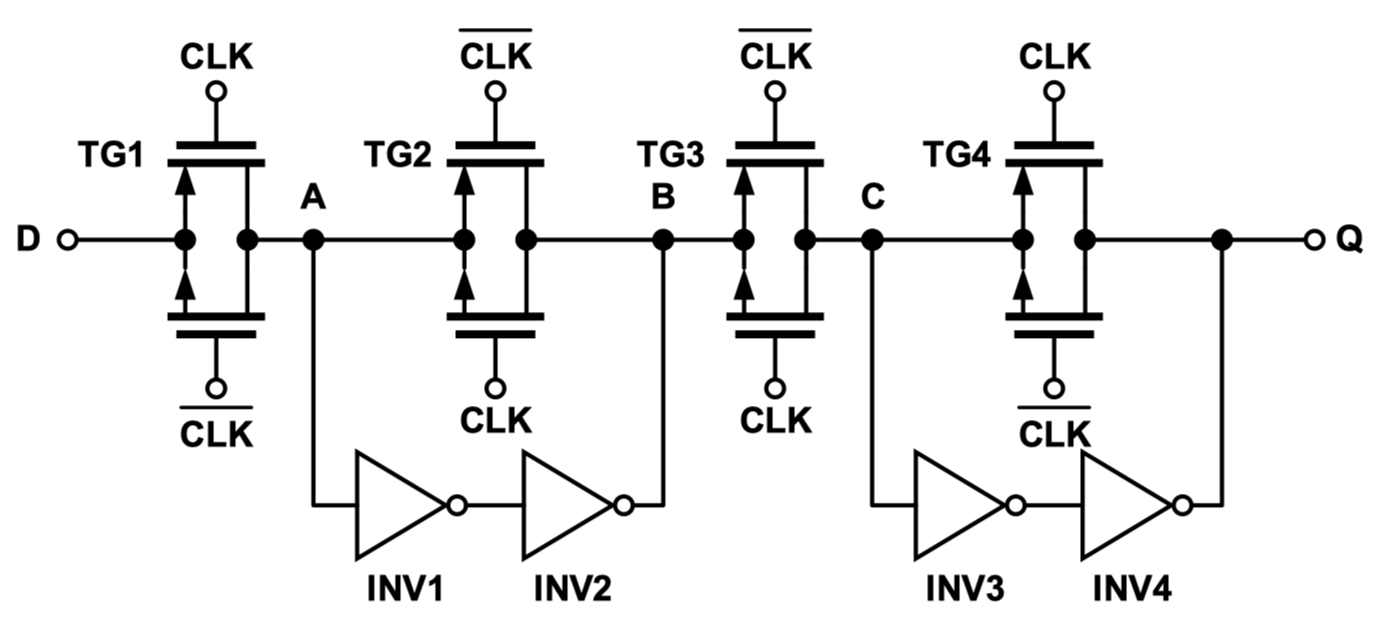

如上图所示,传输门主从锁存器 (Transmission Gate Master-Slave Latch)克服了传输门锁存器需要定期刷新的缺点。

该结构中,传输门 TG1、TG2 和反相器 INV1、INV2 构成了第一级主锁存器;传输门 TG3、TG4 和反相器 INV3、INV4 构成第二级从锁存器。

CLK 由高变低时:传输门 TG1、TG4 打开,传输门 TG2、TG3 关闭。

由于 TG1 打开,TG2关闭,输入信号路径:D -> TG1 -> A -> INV1 -> INV2 -> B,此时一级主锁存器将信号输入 D 传至输出端 B 点;

由于 TG3 关闭,TG4 打开,因此 C 点电平不受 B 点影响,路径为:C -> INV3 -> INV4 -> Q -> TG4 -> C,此时二级从锁存器形成一个稳定的锁存回路,输出端 Q 保持上一次的电平不变。

CLK 由低电平变高电平时:与上面 CLK 由高变低时的情况相反,传输门 TG1、TG4 关闭,传输门 TG2、TG3 打开。

相应的,一级主锁存器形成一个锁存回路,输出 B 点保持上次电平不变;

二级从寄存器将 B 点信号传输至 Q 点。

时钟控制 CMOS 主从锁存器

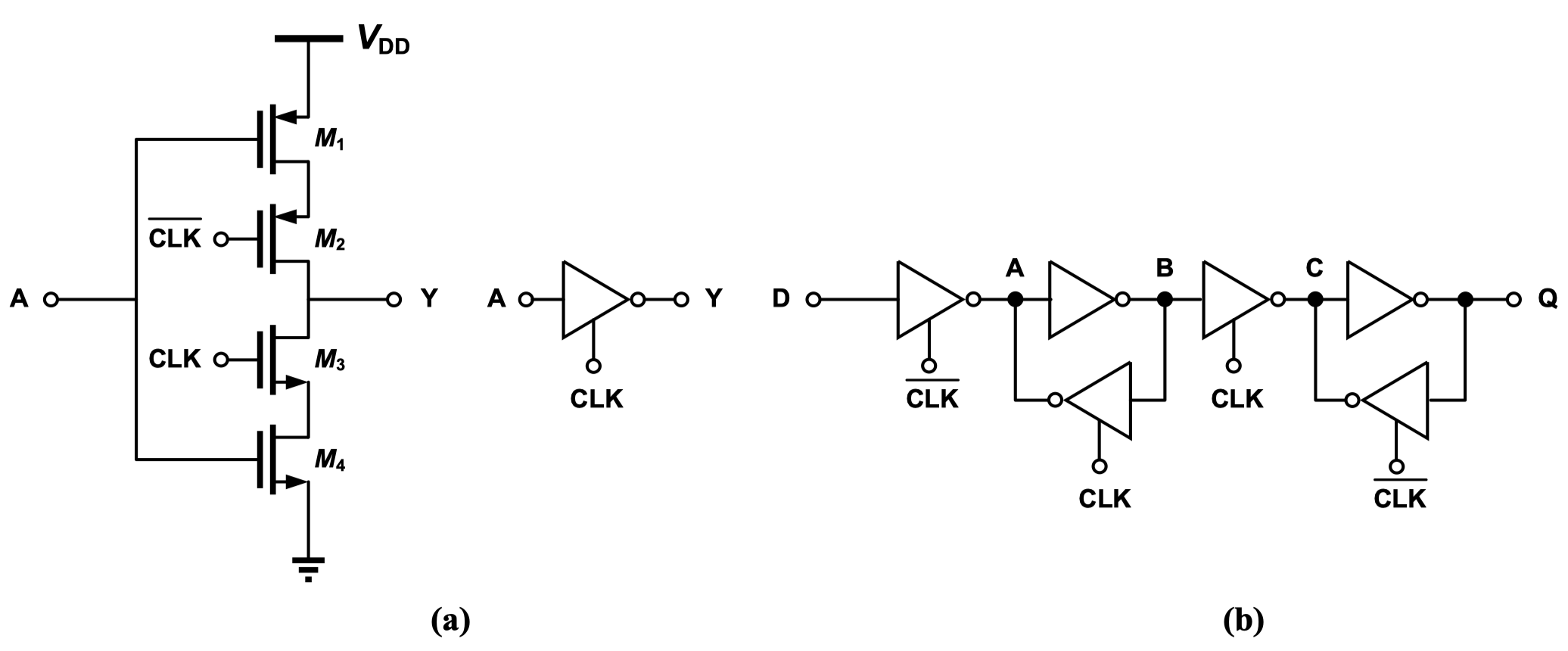

时钟控制 CMOS 主从锁存器 (Clocked CMOS Master-Slave Latch) 是在传输门主从锁存器的基础上发展而来,其主要变化是将传输门锁存器中的传输门和反相器合二为一,构成了如上图 (a) 所示的时钟控制反相器,从而简化了版图,提升了主从锁存器的工作速度。

(具体分析) 待完成

共源共栅电压切换逻辑主从锁存器

一种基于共源共栅电压切换逻辑的主从锁存器 (Cascode Voltage Switch Logic Master-Slave Latch) 如上图所示,\(M_1 \sim M_6\) 构成了一级主锁存器,\(M_7 \sim M_{12}\) 构成二级从锁存器。\(M_1\) 和 \(M_2\) 是一级主锁存器的再生式管对 (???),\(M_{11}\) 和 \(M_{12}\) 是第二极从锁存器中的再生式管对。

以第一级主锁存器为例,介绍其工作原理。

CLK 由低变高时,M5、M6 打开;

若输入 D 为高电平,M3 打开,M4 关闭;

A 点电平下降,B 点电平上升;

A 点电平下降控制 M2 逐渐打开,使 B 点电平更快地上升;

B 点电平下降控制 M1 逐渐关闭,使 A 点电平更快地下降;

最终 A 点下降至地电平,B 点上升至 \(V_{DD}\) 电平。

若输入 D 为低电平,则情况相反,A 点上升至 \(V_{DD}\) 电平,B 点下降至地电平。

CLK 由高变低时,M5、M6 关闭,A、B 点通过 M1、M2 维持前一刻电平不变。

一级主锁存器与二级从锁存器交替工作,形成了一个完整的共源共栅电压切换逻辑主从锁存器。

真单相时钟主从锁存器

真单相时钟主从锁存器 (True Single-Phase Clock Master-Slave Latch) 是在时钟控制 CMOS 主从锁存器的基础上简化而来,主要是省略了同相锁存器,完全以节点寄生电容来存储电平。真单相时钟主从锁存器结构简单、MOS 管数量少、工作速度高、功耗低,特别适用于高速分频器。

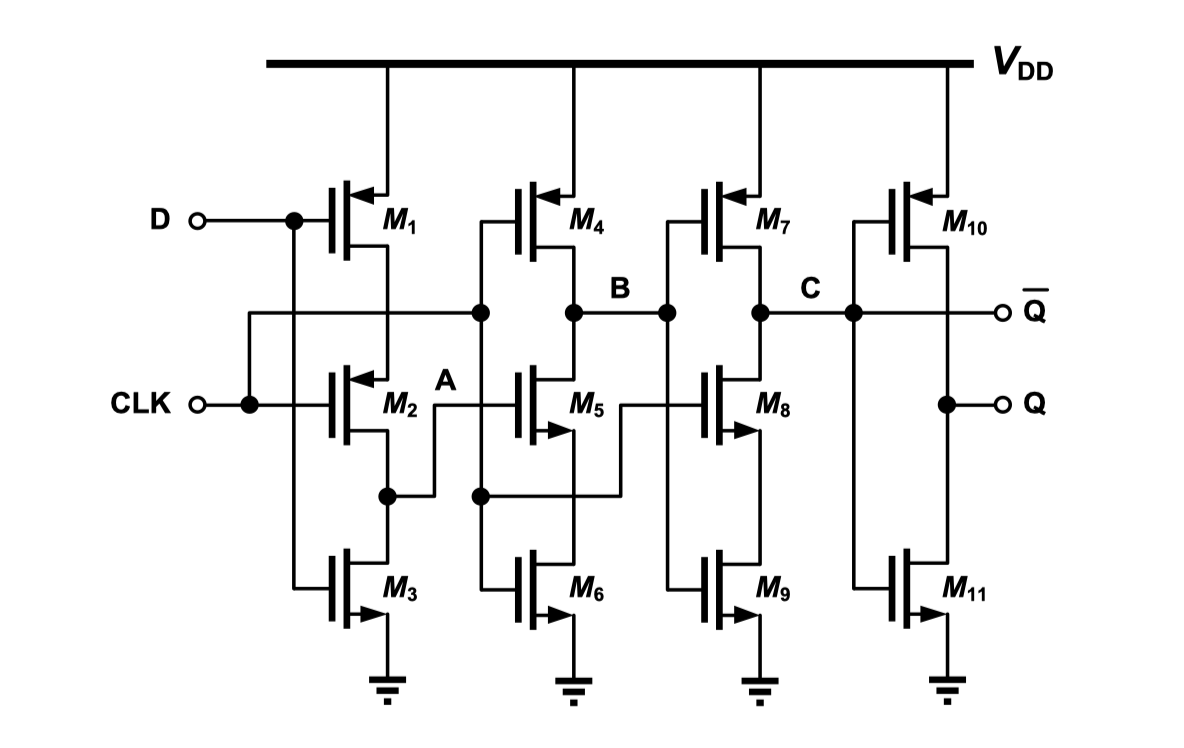

常用的一种真单相时钟主从锁存器结构如上图所示:\(M_1 \sim M_3\) 构成第一级时钟控制反相器,\(M_4 \sim M_6\) 构成第二级时钟控制反相器,\(M_7 \sim M_9\) 构成第三级时钟控制反相器,\(M_{10}\) 和 \(M_{11}\) 构成输出反相器。

CLK 由高电平变低电平后:

第一级时钟控制反相器输出 A 跟随数据输入 D;

第二级时钟控制反相器输出 B 被拉伸至 \(V_{DD}\);

M7 和 M8 分别被 B 和 CLK 关闭,第三级时钟控制反相器输出 C 维持前一时刻电平不变。

CLK 由低电平变高电平后,输入信号 D 需要维持不变 (保证数据输入端在 \(T_S\) 之前建立完毕),A 点电平与 D 点相同:

若 A 点为高电平,B 点被拉低至地电平;若 A 点为低电平,M4、M5 关闭,B 点维持高电平不变;这样实现了 B 点反向跟随 A 点电平;

此时 M8 被 CLK 打开,输出信号 \(\overline{Q}\),再经过 M10、M11组成的反相器输出信号 \(Q\)。

电流模型主从锁存器

电流模型主从锁存器 (Current Mode Logic Master-Slave Latch) 本质上是一个模拟分频器,其 MOS 管的静态工作点均位于饱和区且有尾电流,因此无论该锁存器有没有输入信号,其功耗都是一定的。相比于上述的 CMOS 逻辑锁存器,电流模型主从锁存器的功耗虽然较大,但其工作频率有很大优势,因此在超高速分频器中有广泛应用。

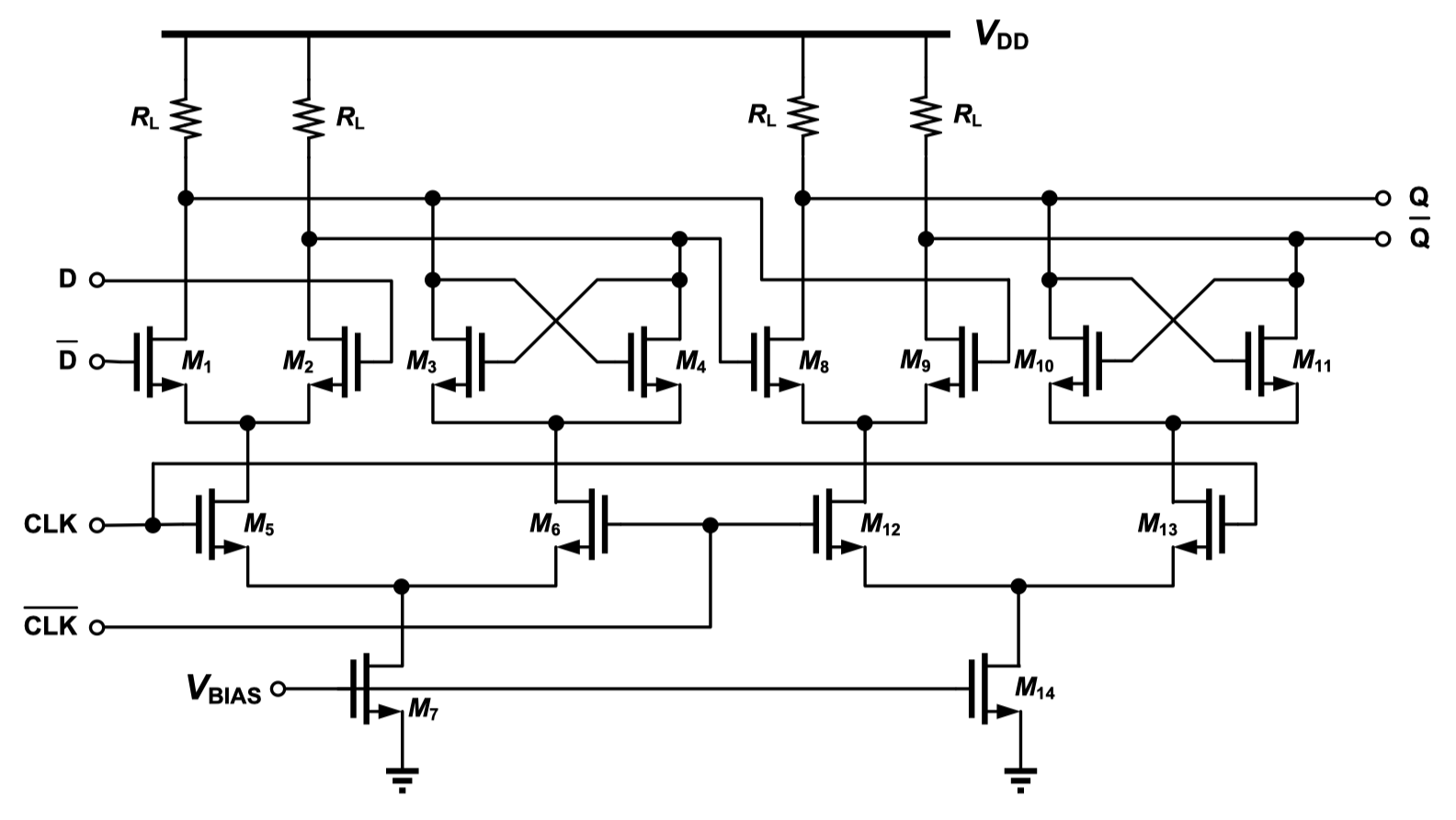

电流模型主从锁存器的结构如上图所示,由两个相同的电流模型锁存器串联组成。

先对其左半部分分析:

M1、M2 为一对差分信号放大管,M3、M4 为一对交叉信号锁存管,M5、M6 为一对查分时钟放大管。

CLK 为高电平时:

M5 导通,M6 截止;

差分信号放大管 M1、M2 对差分输入信号 D 进行采样放大;

交叉信号锁存管 M3、M4 处于无效状态。

CLK 为低电平时:

M5 截止、M6 导通;

差分信号放大管 M1、M2 处于无效状态;

交叉信号锁存管 M3、M4 形成正反馈,开始锁存被采样信号。

右半部分与左半部分结构相同,差分管 M12、M13 的输入信号与 M5、M6 的输入信号时钟反相。

Cadence 仿真

待完成