在 Ubuntu20.04 上安装 Cadence IC617 & MMSIM151 & calibre2015 & INCISIVE152 & ADS2020U2,理论上也适用于其他的 Ubuntu 或 Linux 系统.

Power Amplifier -- 基础知识

无线发射机结构

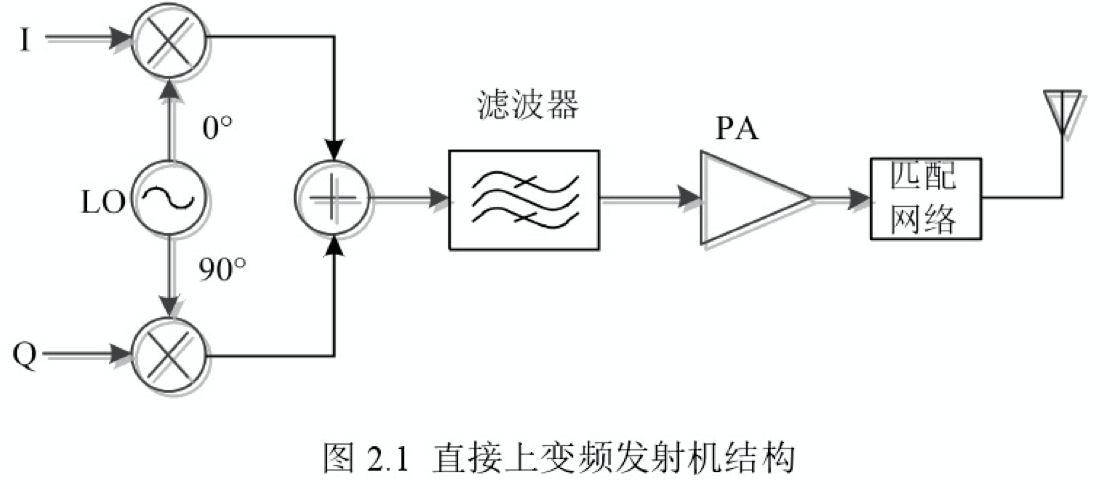

无线发射机按结构类型主要分为三种:直接上变频、超外插和直接数字调制。

上图为直接上变频结构,通过一次变频将 I、Q 两路基带信号变为射频信号。

- 优点:

- 结构简单;

- 能较好得抑制镜像的产生;

- 缺点:

- 工作在射频上的两个混频器需要消耗很大电流;

- 当振荡器和输出处于同一频率时,高频载波馈通和注入锁定 (Injection) 是两个可能出现的问题;

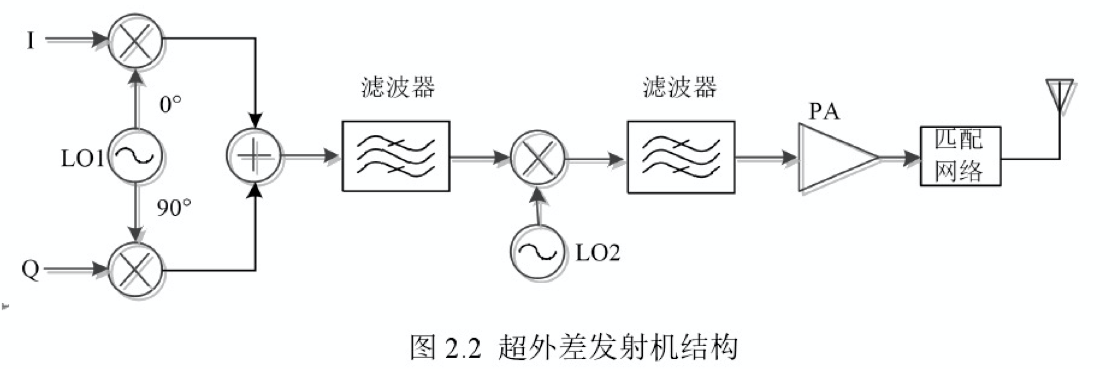

上图为超外差结构,其将数字调制上变频产生的信号再与射频前端的本振进行一次上变频,最后送入功放。

- 优点:

- 该发射机在本振和功放之间加入一个滤波器,具有良好的隔离度;

- 缺点:

- 与直接上变频相比,由于采用了两次上变频,复杂度较高;

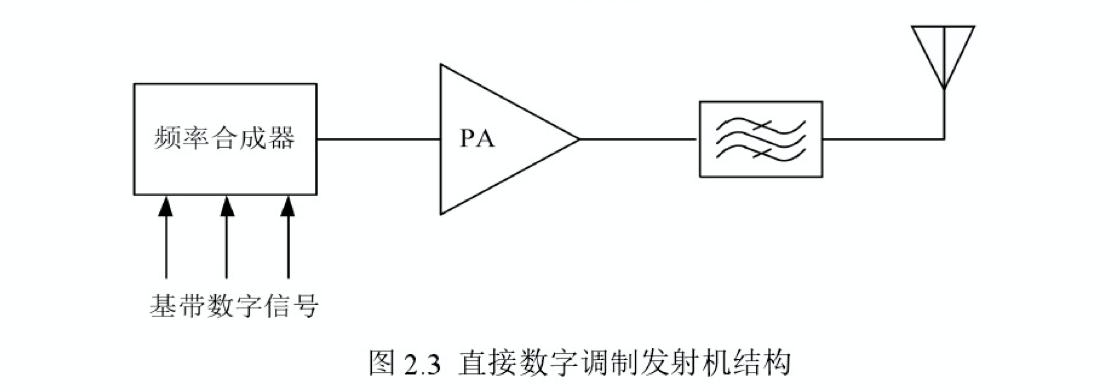

上图为直接数字调制结构,直接将频率合成器的输出送入到功放。

功率放大器的主要技术指标

输出功率

功率附加效率

线性度

功率放大器的分类

功率放大器按晶体管的工作特性可以分为线性功率放大器和开关功率放大器。

线性化技术

目前针对高功率功放提高线性度的方法主要有:功率回退法 (Power Back-off)、前馈法 (Feedforward)、负反馈技术 (Feedback)、预失真技术 (Predistortion)、包络消除与恢复 (Envelope Elimination and Restoration)等。

匹配补偿技术

功率合成技术

VMware Fusion 上为虚拟机设置静态 IP

Cadence ASM Tutorial

最近接触了 Verilog-A。记录一下 Cadence AMS-Designer 数模混合的仿真过程。需要用到的软件有 Cadence IC617, INCISIVE152。

使用 VSCode 编写 LaTeX — Mac 篇

之前在 Mac 上写 LaTex,一直用 Sublime 编写,用 TexPad 编译,TexPad 虽然很好用,界面也很好看,然而它是付费软件,一直用着**版总觉得心里过意不去,就想着替代的方案。

LaTex 可以直接用命令编译,可以写一个脚本,把编译命令放在里面,为了之前写本科毕业论文就是这样做的,然而这样还是不太方便,太 Geek 了。

直到我把文本编辑器从 Sublime 换成 VSCode 后,发现 VSCode 真是太强大了,可以把 LaTex 编写和编译都一起做了,方法如下。

Delta-Sigma Modulator (3) — MASH & HK-MASH & SP-MASH

MASH & HK-MASH & SP-MASH 对比

Delta-Sigma Modulator (2) — Simulink Simulation

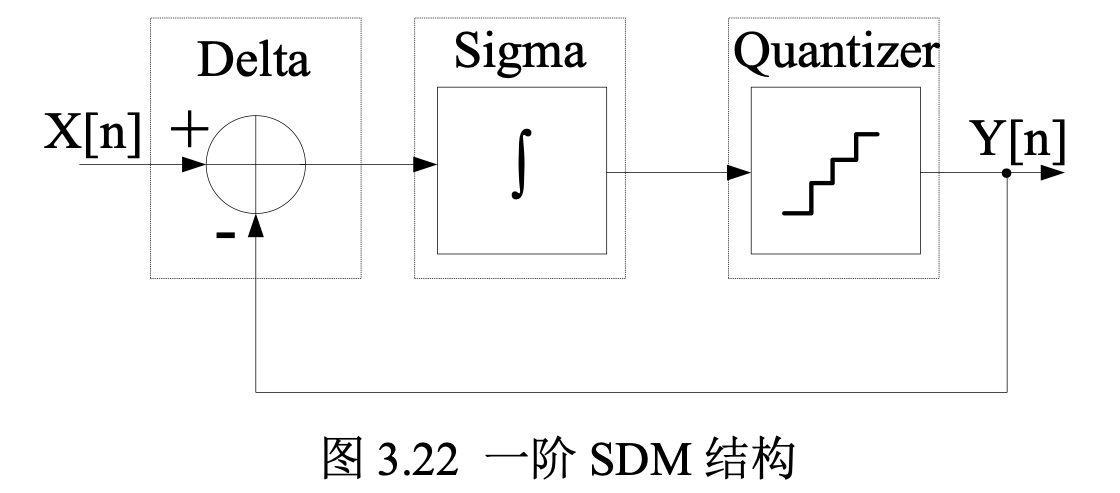

Delta-Sigma Modulator

整数分频锁相环中,生成频率的最小分辨率为参考频率,为了提高分辨率就要降低参考时钟的频率;而锁相环的带宽通常要小于参考频率的 \(1/10\), 因此整数分频锁相环的带宽受分辨率的限制只能很窄。

目前主流的有两种方案解决整数分频锁相环中分辨率和带宽矛盾的问题:欠采样整数型锁相环和分数型锁相环。

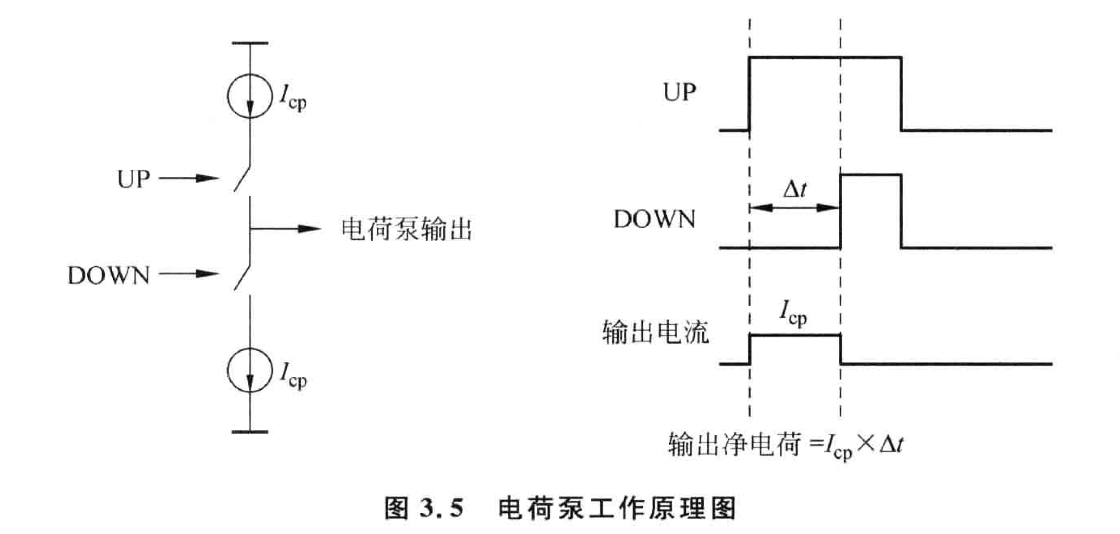

PLL-CP

TSPC

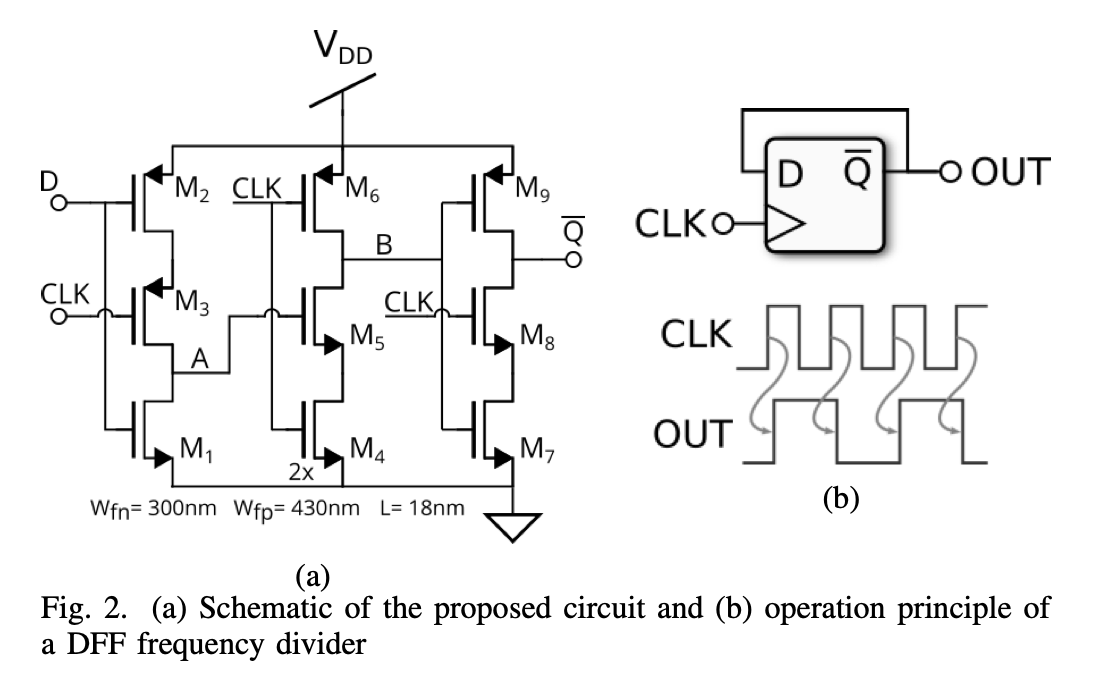

在 PLL 中,分频器负责将较高频率的 VCO 输出信号转换为与基准频率相近的信号,以进行相位比较。分频器通常消耗 PLL 中 VCO 之后的大部分功率,因此设计出低功耗的分频器有助于降低 PLL 的功耗。在高频中,注入锁定分频器 (injection-locked frequency divider, ILFD) 和再生分频器 (regenerative dividers) 比较常见。而基于 D 触发器 (D flip-flop, DFF) 的分频器由于其工作速度的限制通常用于预分频之后的低频率的分频。与高频分频器相比,DFF 分频器具有更低的功耗和更高的锁定范围。在 DFF 中,真单相时钟控寄存器 (true single phase clock, TSPC) 仅使用单相时钟,避免了时钟重叠的影响。